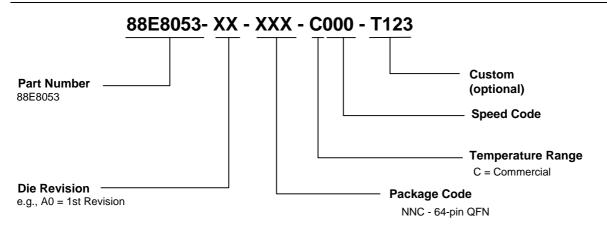

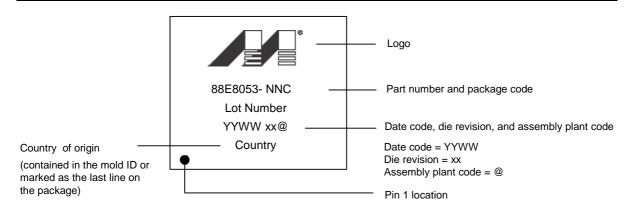

#### **OVERVIEW**

The single-chip PCI Express based 88E8053 device integrates the Marvell<sup>®</sup> market-leading Gigabit PHY with the proven Marvell Gigabit MAC and SERDES cores, delivering an ultra-small form factor and high performance. Delivered with the industry's most comprehensive software driver suite, this Yukon device is ideally suited for LAN on motherboard (LOM) and Network Interface Card (NIC) applications. The 88E8053 device is compliant with the PCI Express 1.0a specification. Offered in a 9 x 9 mm, 64-pin QFN package, the 88E8053 reduces board space required for Gigabit LOM implementation significantly.

The device is optimized for maximum throughput and low CPU utilization. A 48 KB on-chip buffer eliminates the need for any external memory. Packet processing tasks such as TCP segmentation, VLAN insertion and removal, TCP/UDP/IP checksum calculation and checking are all performed on-chip. These offloads along with interrupt moderation schemes reduce CPU utilization and improve the overall system performance.

The 88E8053 device incorporates advanced power management schemes, enabling energy efficient operation. With features such as Wake on LAN and Smart Power Down in the absence of link it is well suited for client applications including mobile PCs.

The 88E8053 Yukon device incorporates the Marvell Virtual Cable Tester™ (VCT™) technology for advanced cable diagnostics. VCT enables IT managers to pinpoint the location of cabling issues down to a meter or less, reducing network installation and support costs.

The device comes with a comprehensive suite of software device drivers for all desktop operating systems, including Microsoft® Windows® 98/Me, NT, 2000, and XP, Linux, and Novell Netware. A complete hardware reference design is provided for a quick implementation.

#### **FEATURES**

#### **PCI EXPRESS FEATURES**

- PCI Express base specification 1.0a compliant

- x1 PCI Express interface with 2.5 GHz signaling

- Active state power management (L0s) support

- Advanced error reporting

#### MAC / PHY FEATURES

- · Configurable 48 KB deep buffer

- · Descriptor bursting and caching

- Message signaled interrupts

- TCP segmentation offload / Large-send support

- On-chip VLAN insertion and removal

- · TCP, IP, UDP Checksum offload

- Interrupt moderation

- Jumbo frame support

- Compliant to 802.3x flow control support

- IEEE 802.1p and 802.1q support

- 10/100/1000 IEEE 802.3 compliant

- Automatic MDI/MDIX crossover at all speeds

#### MANAGEABILITY

- Wake On LAN (WOL) power management support

- Compliant to ACPI 2.0 specification

- Out of the box WOL support

- Wake On Link

- Serial Peripheral Interface (SPI) for remote boot (PXE 2.1)

- · Smart power down when link is not detected

- Marvell Virtual Cable Tester<sup>™</sup> (VCT) for advanced cable diagnostics

#### OTHER FEATURES

- LOM disable pin

- Power regulator outputs for 2.5V and 1.2V supplies

- Two Wire Serial Interface (TWSI) for VPD EEPROM

- 9 mm x 9 mm, 64-pin QFN package

# **Table of Contents**

| SEC  | TION 1              | . SIGNAL DESCRIPTION                          | 7  |

|------|---------------------|-----------------------------------------------|----|

| 1.1  | 64-Pin              | QFN Pinout (Top View)                         | 7  |

| 1.2  | <b>Pin De</b> 1.2.1 | Pin Type Definitions                          |    |

| SEC  | TION 2              | FUNCTIONAL DESCRIPTION                        | 14 |

| 2.1  | Overv               | iew                                           | 14 |

| 2.2  | PCI-E               | xpress Features                               | 16 |

| 2.3  | SPI FI              | ash Memory                                    | 18 |

| 2.4  |                     | ash Memory Loader                             |    |

| 2.5  |                     | EEPROM                                        |    |

| 2.6  | TWSI                | EEPROM Loader                                 | 23 |

| 2.7  |                     | n Go Unit                                     |    |

| 2.8  | Interru             | ıpts                                          | 25 |

|      | 2.8.1               | IRQ Moderation Timer                          |    |

|      | 2.8.2               | Message Signaled Interrupts (MSI)             | 28 |

| 2.9  | Buffer              | Management Units (BMU)                        | 28 |

|      | 2.9.1               | Format of Descriptor and Status List Elements |    |

|      | 2.9.2               | TCP/UDP Processing of RX and TX BMU           |    |

|      | 2.9.3               | Prefetch Unit                                 | 40 |

|      | 2.9.4               | Status BMU                                    |    |

|      | 2.9.5               | Polling Unit                                  | 45 |

| 2.10 | Timer               |                                               | 46 |

| 2.11 | Times               | tamp Timer                                    | 46 |

| 2.12 | Wake                | on LAN                                        | 47 |

|      |                     | Wake up Frame Logic                           |    |

|      | 2.12.2              | Magic Packet frame detect                     | 49 |

|      | 2.12.3              | Link Change Monitoring                        | 49 |

| 2.13  | GMAC                                                  | 50    |

|-------|-------------------------------------------------------|-------|

| 2.14  | PHY                                                   | 51    |

| 2 1 5 | LEDs                                                  | E4    |

| 2.15  | 2.15.1 LED Capabilities of 88E8053                    |       |

|       | ·                                                     |       |

| 2.16  | VPD                                                   | 52    |

| 2.17  | TWSI Interface                                        | 52    |

| 2 18  | Parity Generation/Check                               | 52    |

| 2.10  | 2.18.1 Internal byte based parity checking/generating |       |

|       | 2.18.2 Parity Checking/Generating on PCI as target    |       |

|       | 2.18.3 Parity Checking/generating on PCI as master    |       |

| SEC   | TION 3. REGISTER DESCRIPTION                          | 54    |

| 3.1   | Legend                                                |       |

|       | <b>G</b>                                              |       |

| 3.2   | PCI-Express Configuration Register File               |       |

|       | 3.2.1 Overview and Address Map                        |       |

|       | 3.2.2 Registers of PCI Header Region                  |       |

|       | 3.2.3 Registers of Header Region                      |       |

|       | 3.2.4 Registers of Device Dependent Region            | 69    |

| 3.3   | Control Register File                                 | 108   |

|       | 3.3.1 Overview and Address Map                        |       |

|       | 3.3.2 Registers                                       |       |

| 3.4   | GMAC Registers                                        | 213   |

|       | 3.4.1 MAC Register Definitions                        |       |

|       |                                                       |       |

| SEC   | TION 4. ELECTRICAL SPECIFICATIONS                     | 239   |

| 4.1   | Absolute Maximum Ratings                              | 239   |

| 4.2   | -                                                     |       |

| 4.2   | Recommended Operating Conditions                      |       |

| 4.3   | Package Thermal Information                           |       |

|       | 4.3.1 Thermal Conditions for 64-pin QFN Package       | 241   |

| 4.4   | DC Electrical Characteristics                         | 242   |

|       | 4.4.1 Current Consumption AVDDL                       |       |

|       | 4.4.2 Current Consumption VDD                         |       |

|       | 4.4.3 Current Consumption VDDO_TTL                    |       |

|       | 4.4.4 Digital Operating Conditions                    |       |

|       | 4.4.5 IEEE DC Transceiver Parameters                  |       |

| 4.5   | AC Timing Reference Values                            | 246   |

| 4.6   | AC Electrical Specifications                          | 247   |

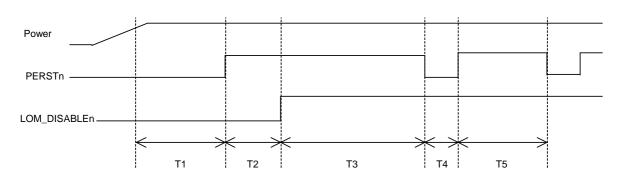

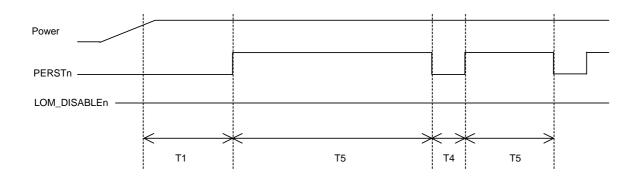

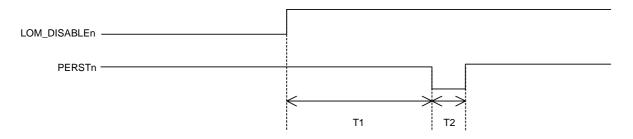

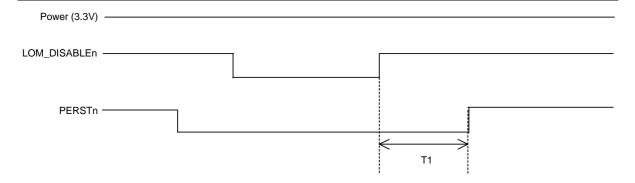

|       | 4.6.1 Reset Timing                                    |       |

|       |                                                       | ← ⊤ / |

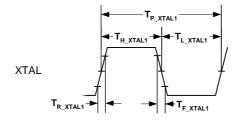

|     | 4.6.3  | Clock Timing                            | 249 |

|-----|--------|-----------------------------------------|-----|

|     | 4.6.4  | PCI Express Timing                      | 250 |

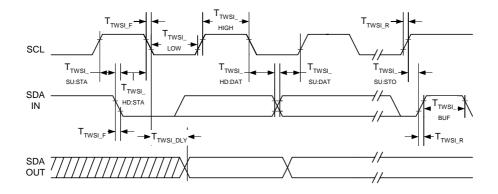

|     |        | Two-Wire Serial Interface (TWSI) Timing |     |

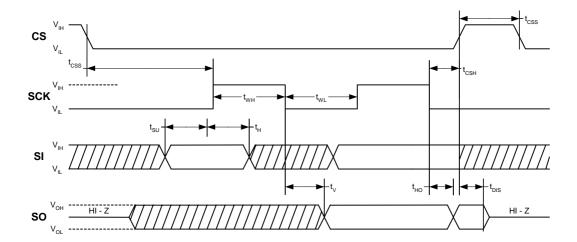

|     |        | SPI FLash Memory Interface Timing       |     |

|     | 4.6.7  | SMBUS Specifications                    | 255 |

|     |        |                                         |     |

| 4.7 | IEEE / | AC Parameters                           | 256 |

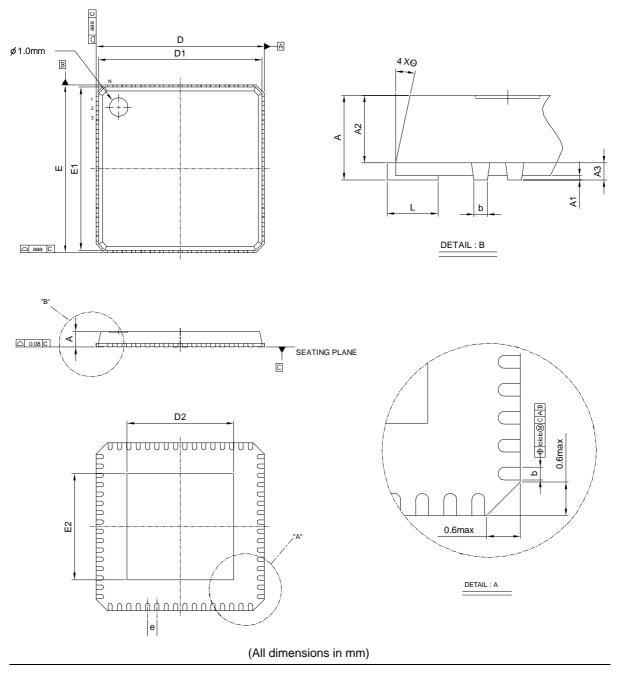

|     |        | S. MECHANICAL DRAWINGS                  |     |

| SEC | TION 5 |                                         | 257 |

# **Section 1. Signal Description**

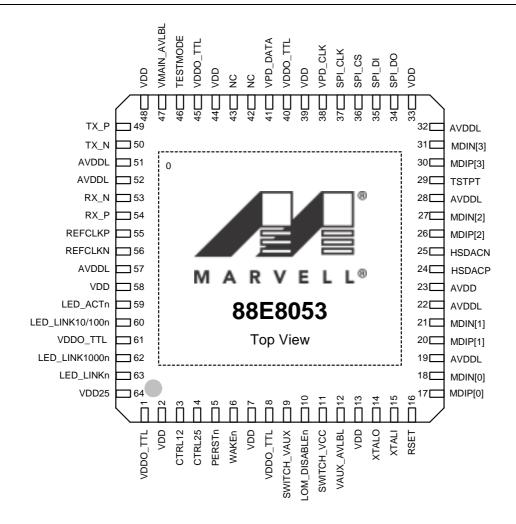

## 1.1 64-Pin QFN Pinout (Top View)

The 88E8053 device is manufactured in a 64-pin QFN, 9 x 9 mm package.

Figure 1: 88E8053 64-Pin QFN Package (Top View)

# 1.2 Pin Description

## 1.2.1 Pin Type Definitions

| Pin Type | Definition            |

|----------|-----------------------|

| Н        | Input with hysteresis |

| I/O      | Input and output      |

| 1        | Input only            |

| 0        | Output only           |

| PU       | Internal pull-up      |

| PD       | Internal pull-down    |

| D        | Open drain output     |

| Z        | Tri-state output      |

| mA       | DC sink capability    |

Table 1: PCI Express Signals

| 88E8053<br>Pin # | Pin Name           | Pin<br>Type | Description                                                                                                                                                                                            |

|------------------|--------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 49<br>50         | TX_P<br>TX_N       | O Analog    | PCI Express Transmit line (positive and negative pair). 2.5 GHz low-voltage pair.                                                                                                                      |

| 54<br>53         | RX_P<br>RX_N       | I Analog    | PCI Express Receive line (positive and negative pair).  2.5 GHz low-voltage pair.                                                                                                                      |

| 6                | WAKEn              | 0           | PCI Express wake signal. Driven low to re-activate the PCI Express lin hiearchy's main power rails and reference clocks. (Open collector, active low.) Multiplexed to the same pin as PCI signal PMEn. |

| 55<br>56         | REFCLKP<br>REFCLKN | I Analog    | PCI Express platform reference clock (differential pair of positive and negative signal lines).  100 MHz low-voltage interface.                                                                        |

| 5                | PERSTn             | I           | PCI Express fundamental reset. Asserted 100 ms after power rails are within specifications.                                                                                                            |

Table 2: Media Dependent Interface (PHY)

| 88E8053<br>Pin # | Pin Name           | Pin<br>Type | Description                                                                                                                                                                                                                                                                                                                                                                                            |

|------------------|--------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 17<br>18         | MDIP[0]<br>MDIN[0] | I/O, D      | Media Dependent InterfacePositive/Negative[0].  In 1000BASE-T mode in MDI configuration, MDIP/N[0] correspond to BI_DAP/N. In MDIX configuration, MDIP/N[0] correspond to BI_DBP/N.  In 100BASE-TX and 10BASE-T modes in MDI configuration, MDIP/N[0] are used for the transmit pair. In MDIX configuration, MDIP/N[0] are used for the receive pair.  MDIP/N[0] should be tied to ground if not used. |

| 20 21            | MDIP[1]<br>MDIN[1] | I/O, D      | Media Dependent InterfacePositive/Negative[1].  In 1000BASE-T mode in MDI configuration, MDIP/N[1] correspond to BI_DAP/N. In MDIX configuration, MDIP/N[1] correspond to BI_DBP/N.  In 100BASE-TX and 10BASE-T modes in MDI configuration, MDIP/N[1] are used for the transmit pair. In MDIX configuration, MDIP/N[1] are used for the receive pair.  MDIP/N[1] should be tied to ground if not used. |

| 26<br>27         | MDIP[2]<br>MDIN[2] | I/O, D      | Media Dependent InterfacePositive/Negative[2].  In 1000BASE-T mode in MDI configuration, MDIP/N[2] correspond to BI_DAP/N. In MDIX configuration, MDIP/N[2] correspond to BI_DBP/N.  In 100BASE-TX and 10BASE-T modes, MDIP/N[2] are not used.  MDIP/N[2] should be tied to ground if not used.                                                                                                        |

| 30<br>31         | MDIP[3]<br>MDIN[3] | I/O, D      | Media Dependent InterfacePositive/Negative[3].  In 1000BASE-T mode in MDI configuration, MDIP/N[3] correspond to BI_DAP/N. In MDIX configuration, MDIP/N[3] correspond to BI_DBP/N.  In 100BASE-TX and 10BASE-T modes, MDIP/N[3] are not used.  MDIP/N[3] should be tied to ground if not used.                                                                                                        |

Table 3: TWSI Interface (For Connection to TWSI EEPROM)

| 88E8053<br>Pin # | Pin Name | Pin<br>Type   | Description                                                                                               |

|------------------|----------|---------------|-----------------------------------------------------------------------------------------------------------|

| 38               | VPD_CLK  | O, D, PU      | TWSI bus clock line to serial EEPROM (with VPD/Boot data). VPD_CLK contains an internal pull-up resistor. |

| 41               | VPD_DATA | Bi-Dir,<br>PU | TWSI bus data line to serial EEPROM (with VPD/Boot data). VPD_DATA contains an internal pull-up resistor. |

#### Table 4: SPI Flash Memory Interface

| 88E8053<br>Pin # | Pin Name | Pin<br>Type | Description                                                                               |

|------------------|----------|-------------|-------------------------------------------------------------------------------------------|

| 34               | SPI_DO   | 0           | Data line leading to the SPI Flash Memory. SPI_DO contains an internal pull-up resistor.  |

| 35               | SPI_DI   | I           | Data line coming from the SPI Flash Memory. SPI_DI contains an internal pull-up resistor. |

| 37               | SPI_CLK  | 0           | Clock line for SPI Interface. SPI_CLK contains an internal pull-up resistor.              |

| 36               | SPI_CS   | 0           | Chip select for SPI Flash Memory. SPI_CS contains an internal pull-up resistor.           |

### Table 5: Main Clock Interface (PHY)

| 88E8053<br>Pin # | Pin Name | Pin<br>Type | Description                              |

|------------------|----------|-------------|------------------------------------------|

| 15               | XTALI    | 1           | Input from 25 MHz Crystal or Oscillator. |

| 14               | XTALO    | 0           | Output to 25 MHz Crystal.                |

#### Table 6: Analog (PHY)

| 88E8053<br>Pin # | Pin Name         | Pin<br>Type    | Description                                                                                                                                            |

|------------------|------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10               | LOM_<br>DISABLEn | I              | Used in LOM applications. The LOM_DISABLEn pin is active low 0 = LAN on motherboard (LOM) disabled 1 = LOM enabled                                     |

| 12               | VAUX_AVLBL       | 1              | VAUX available signal.                                                                                                                                 |

| 11               | SWITCH_VCC       | 0              | Switch to VCC.                                                                                                                                         |

| 47               | VMAIN_AVLBL      | 1              | VMAIN available signal.                                                                                                                                |

| 9                | SWITCH_VAUX      | 0              | Switch to Vaux.                                                                                                                                        |

| 24<br>25         | HSDACP<br>HSDACN | Analog<br>O, D | PHY Test pin. These pins are used for debug only. If debug is not important and there are board space constraints, these pins should be left floating. |

| 16               | RSET             | Analog<br>I    | PHY Constant voltage reference. External 5.0 k $\Omega$ 1% resistor connection to VSS.                                                                 |

| 4                | CTRL25           | O Analog       | Regulator Control. This signal controls an external PNP transistor to generate the 2.5V power supply.                                                  |

| 3                | CTRL12           | O Analog       | Regulator Control. This signal controls an external PNP transistor to generate the 1.2V power supply.                                                  |

#### Table 7: LED Interface

| 88E8053<br>Pin # | Pin Name            | Pin<br>Type | Description                                                                                                              |

|------------------|---------------------|-------------|--------------------------------------------------------------------------------------------------------------------------|

| 59               | LED_ACTn            | TTL, D      | Parallel LED activity indicator. Active low.                                                                             |

| 60               | LED_<br>LINK10/100n | TTL, D      | Parallel LED output for 100BASE-T link or speed. If the LED_LINK10/100 pin is active, it indicates 100 Mbps. Active low. |

| 62               | LED_LINK1000n       | TTL, D      | Parallel LED output for 1000BASE-T link. Active low.                                                                     |

| 63               | LED_LINKn           | TTL, D      | Parallel LED output for 10/100/1000BASE-T link. Active low.                                                              |

#### Table 8: Test Pins

| 88E8053<br>Pin # | Pin Name | Pin<br>Type | Description                                      |

|------------------|----------|-------------|--------------------------------------------------|

| 46               | TESTMODE | I, PD       | Selection of internal Test. (Default pull-down.) |

| 29               | TSTPT    | 0           | Analog test point.                               |

Table 9: Power & Ground

| 88E8053<br>Pin #                           | Pin Name | Pin<br>Type | Description                                                                                           |  |

|--------------------------------------------|----------|-------------|-------------------------------------------------------------------------------------------------------|--|

| 64                                         | VDD25    | Power       | Power to TTL I/Os. 2.5V                                                                               |  |

| 19<br>22<br>28<br>32<br>51<br>52<br>57     | AVDDL    | Power       | Analog Power. 2.5V - Copper                                                                           |  |

| 23                                         | AVDD     | Power       | Analog Power. 2.5V (For 3GIOs)                                                                        |  |

| 1<br>8<br>40<br>45<br>61                   | VDDO_TTL | Power       | Power to TTL I/Os. 3.3V (Pin 8 can be used as power to VAUX 3.3V - see Application Note for details.) |  |

| 2<br>7<br>13<br>33<br>39<br>44<br>48<br>58 | VDD      | VDD         | Power. 1.2V                                                                                           |  |

| 0                                          | EPAD     | Ground      | Ground.                                                                                               |  |

#### Table 10: No Connect

| 88E8053<br>Pin # | Pin Name | Pin<br>Type | Description                                   |  |

|------------------|----------|-------------|-----------------------------------------------|--|

| 42<br>43         | NC       |             | No connect. These pins must be left floating. |  |

## **Section 2. Functional Description**

### 2.1 Overview

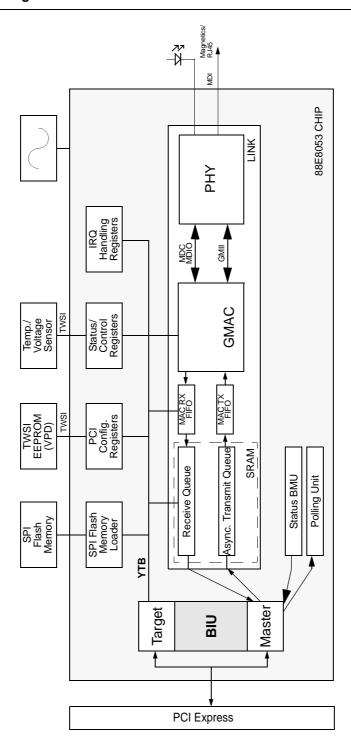

This Single Link Gigabit Ethernet Controller device comes with a PCI Express interface and Gigabit Ethernet cable connectivity. The device integrates PCI Express interface, BMUs, RAM, MAC, PHY, and SERDES cores.

An optional 128/256 kByte SPI Flash Memory holds Bootcode and Configuration Data. The Configuration Data is read by the SPI Flash Memory Loader after POWER ON RESET. All writable registers on the PCI device, may be reloaded from the SPI Flash Memory. The SPI Flash Memory is required if other ROM options are not available for bootcode (PXE). The VPD data are stored within an onboard TWSI EEPROM. In absence of this TWSI EEPROM the VPD data may be stored within the SPI Flash Memory.

The PCI device is controlled by the system's CPU through the PCI Target Interface. The description of all accessible registers is concentrated in the chapters **Configuration Register File** and **Control Register File**. Most registers are controlled only at initialization time.

Receive/transmit data and descriptors are transferred to/from system memory over the PCI Interface controlled by the Buffer Management Units (BMU). The GE Link has a Receive Queue, and a asynchronous Transmit Queue. These two queues run independently. The BMU manages the data transfer to/from system memory. This is controlled by the system's CPU through descriptors allocating memory buffers. Descriptors are organized in chained lists.

The PCI FIFO provides data/space for burst transfers. The Rambuffer Control Logic organizes programmable Rambuffer areas in the internal SRAM as FIFOs for buffering of receive/transmit data (e.g. in order to prevent receive overflows). It controls the dataflow between its PCI FIFO and MAC FIFO through the allocated Rambuffer. Packets may be transferred in Flow Through Mode or Store & Forward Mode.

PCI Accesses are arbitrated in a hierarchical priority scheme. Transfer length is optimized for Cache Line Sizes and best PCI Command usage (descriptors and data). The PCI Master supports fully misaligned transfers of Receive/Transmit Data (descriptors must be located at dword boundaries).

The RAM Interface arbitrates RAM accesses requested by the Rambuffer Control Logics in a rotating priority scheme generally. In some cases the priority scheme is adapted dynamically (e.g. risk of receive overflow, Rate Control on transmit). Re-arbitration takes place on chunk level. Chunk length is programmable, default is 32 qwords.

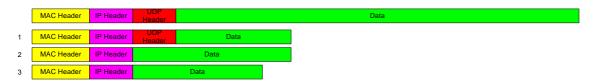

For Transmit Packets a TCP/IP Checksum may be calculated and inserted, on Receive Packets, TCP/IP Checksum is calculated. TCP/IP Checksum Generation/Checking is controlled by the descriptors. TCP/UDP Checksum generation and insertion can be handled also for large fragmented packets. For UDP checksum is calculated over all the appropriate packets and is inserted into the first packet of the sequence.

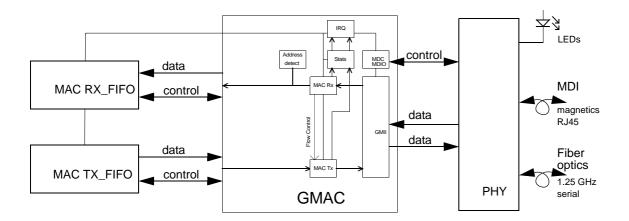

Figure 2 shows the device block diagram.

Page 14

Figure 2: Block Diagram

# 2.2 PCI-Express Features

Table 11 lists the features of the PCI-Express interface.

#### Table 11: General PCI-Express Features

| Feature Name             | Description                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Standard<br>Compliance   | Compliant with PCI-Express Base 1.0a Specification.                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| PCI-Express port         | <ul> <li>2.5 GHz Signaling.</li> <li>X1 link width.</li> <li>Width strapped on reset.</li> <li>Support link reversal and lane polarity reversal.</li> </ul>                                                                                                                                                                                                                                                                               |  |  |  |

| Master transaction types | <ul> <li>Support of up to 8 outstanding NP requests as a master (requester).</li> <li>All Memory transactions, except lock related.</li> </ul>                                                                                                                                                                                                                                                                                            |  |  |  |

| Target transaction types | <ul> <li>Support of 2 outstanding non-posted requests as a target (completer).</li> <li>All Memory transactions, except lock related.</li> <li>I/O transactions - supported only when working in legacy endpoint mode.</li> <li>Configuration transactions - type0 only.</li> <li>Support up to 8B target accesses.</li> </ul>                                                                                                            |  |  |  |

| Message support          | <ul> <li>Interrupt messages.</li> <li>Error messages.</li> <li>PM related.</li> <li>Hot-plug related.</li> <li>Not supported - lock related and vendor specific messages.</li> </ul>                                                                                                                                                                                                                                                      |  |  |  |

| Configuration<br>Space.  | <ul> <li>Extended 4 KB PCI-Express configuration space.</li> <li>Single Function Device.</li> <li>External configuration register file.</li> </ul>                                                                                                                                                                                                                                                                                        |  |  |  |

| Interrupts               | <ul> <li>Support of both MSI and interrupt messages.</li> <li>External BIU master agent is responsible for MSI generation.</li> </ul>                                                                                                                                                                                                                                                                                                     |  |  |  |

| Error Reporting          | <ul> <li>Full support of PCI-Express base-line error reporting.</li> <li>Full support of Advanced error reporting capability.</li> <li>Three error severity levels: Correctable, Uncorrectable - Non-Fatal and Uncorrectable - Fatal.</li> <li>Header logging and pointer to first uncorrectable error.</li> <li>Programmable error severity.</li> <li>PCI error mapping - Mapping of errors to PCI error reporting mechanism.</li> </ul> |  |  |  |

| Address Space            | <ul> <li>Three 64bit memory BARs for internal registers access.</li> <li>One I/O BAR for internal registers access.</li> <li>Expansion ROM BAR.</li> </ul>                                                                                                                                                                                                                                                                                |  |  |  |

| Virtual Channels         | <ul> <li>Support of baseline TC0-VC0 mapping.</li> <li>One virtual channel (VC) hardware resource.</li> </ul>                                                                                                                                                                                                                                                                                                                             |  |  |  |

Table 11: General PCI-Express Features

| Feature Name        | Description                                                                                                                                                |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power<br>Management | <ul> <li>Supported SW directed PM states: L0, L1, L2, L3</li> <li>Supported Active State Link PM states: L0s-Rx.</li> </ul>                                |

|                     | <ul> <li>Support of wake event generation from all device PM states including D3hot.</li> <li>Wake event signalling by WAKE# signal mechanisms.</li> </ul> |

**Table 12: Main PCI-Express Parameters.**

| Feature Name                              | Description |

|-------------------------------------------|-------------|

| Max Payload Size                          | • 128B      |

| Maximum Read Request Size                 | Up to 4 KB  |

| RCB - Read Completion Boundary parameter. | • 128B      |

## 2.3 SPI Flash Memory

The SPI Flash Memory has a size of 128/256 KByte. For future applications SPI Flash Memories up to 1 MByte can be handled.

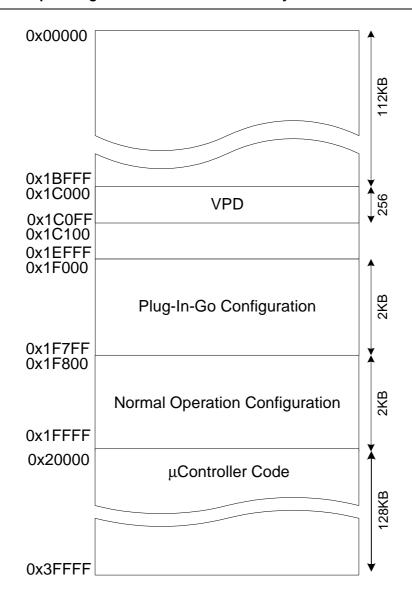

Figure 3: Address Space Organization of SPI Flash Memory

The SPI Flash Memory may be mapped into the memory address space with sizes of 16 KB, 32 KB, 64 KB or 128 KB. The page size is defined by **Pagesize<1:0>** (**Our Register 1**).

If En Eprom (Our Register 1) is not set, the Expansion Rom Base Address Register is not presented to the Configuration Register File, the SPI Flash Memory is not mapped to the memory address space.

The mapped page is selected by setting Page Reg<2:0> (Our Register 1).

The base address is defined in the **Expansion Rom Base Address Register**. The **Expansion Rom Base Address Register** also holds the page size and **ROMEN** which controls enabling of the expansion ROM.

The 4 kBytes sector (0x1F000 - 0x1FFFF) holds data configuring the network adapter after PERSTn.

In absence of the TWSI EEPROM the SPI Flash Memory contains also VPD Data (0x1C000, 0x1C0FF, **SPI Flash Memory VPD Configuration Register**).

Memory accesses to the SPI Flash Memory are read only.

Write operations are completed normally on the bus and the data is discarded.

For programming of the SPI Flash Memory no additional 12V power supply and switching of the programming voltage is required.

The SPI Flash Memory (256 kB) is organized in eight sectors with 32 kBytes each and 128 pages (page = 256 Byte) per sector:

Table 13: Eight SPI Flash Memory Sectors

| Sector Address   | Sector |

|------------------|--------|

| 000000 to 007FFF | 1      |

| 008000 to 00FFFF | 2      |

| 010000 to 017FFF | 3      |

| 018000 to 01FFFF | 4      |

| 020000 to 027FFF | 5      |

| 028000 to 02FFFF | 6      |

| 030000 to 037FFF | 7      |

| 038000 to 03FFFF | 8      |

## 2.4 SPI Flash Memory Loader

The SPI Flash Memory Loader supports the following features:

- Loading of data after PERSTn from the SPI Flash Memory into the Configuration and Control Register File (where needed).

- The loader is capable of accessing potentially all registers in the Control Register File space.

- Register address and data are stored in 8-byte entries in the SPI Flash Memory.

- The registers may be written with dword, word or byte accesses.

- The 8-byte entries are located on 8-byte boundaries starting at address 0x1F800 (or 0x1F000 for Plug-In-Go, configurable within **SPI Flash Memory Loader Control Register**) of the SPI Flash Memory in increasing order. Each entry is marked with a key.

- The selection of Plug-In-Go or normal operation configuration is done depending on the detected power supply by  $V_{AUX}$  or PCI power line.

- If started, the loader reads subsequent entries starting with the initial value of the **Normal Loader Start Address** (Bit 27:16 in **SPI Flash Memory Loader Configuration Register**) or, if Plug In Go, with the value of the **PiG Loader Start Address** (Bit 11:0).

- Loading is started by deassertion of PERSTn or the setting of the SPI loader start bit in the SPI Flash Memory Control Register.

- While loading, accesses to any resource of the network adapter are terminated by Target Retry Cycles.

- The transferred data after PERSTn in this way is limited to fulfill the requirements of PCI bus<sup>1</sup>.

- The command **SPI loader start** is intended for testing purposes only. It is not recommended to reload the **Configuration Register File** by using this command.

Table 14: First 8 byte unit within Normal Operation Configuration Region of SPI Flash Memory

| 31:24         | 23:16         | 15:8     |         | 7:0        | Address |

|---------------|---------------|----------|---------|------------|---------|

| Address/upper | Address/lower | reserved | BE<3:0> | key = 0x55 | 0x1f800 |

| Data<3>       | Data<2>       | Data<1>  |         | Data<0>    | 0x1f804 |

#### Loading Boot-Code:

The boot data can be accessed as byte, word, or dword at a time. All combinations of byte-enables of the PCI specification are supported. There is a cache, which holds 2 consecutive dwords (8 bytes) of data. Initially, there is no valid data in the cache. When a boot access is initiated, consecutive dwords are fetched, starting with the dword containing the requested data. The requested byte/word/dword is forwarded as soon as the dword that contains the accessed address is loaded. The loader doesn't wait for the following dword fetch also to complete. A cache location (dword) is released (declared empty) when byte 4 in that dword is read out. Reading byte 4 may be done by dword/word/byte access. The SPI read continues as long as there is at least one empty location in the cache. This means that, in theory, the SPI memory could be transferred within one single burst throughout a sequential data load. The burst is broken when there is a jump in address or the access over the PCI bus takes too long time and the cache fills up. When requested data is in the cache (hit), data is supplied from the cache and no new SPI access is required. A new SPI access is initiated when there is a miss (requested data is not found in the cache or that dword is currently being fetched). The cache contents are made invalid when the SPI memory is written to.

#### Loading VPD-Data:

If the VPD-Data is in the SPI Flash Memory the whole 256 Byte can be accessed by 8 Read-Cycles to the VPD area (0x1c000 - 0x1c0ff). The data are stored in the lower dword of the cache.

Doc. No. MV-S102130-00, Rev. -- CONFIDENTIAL Copyright © 2004 Marvell

Page 20 Document Classification: Proprietary Information

T<sub>nhfa</sub> PERSTn High to First configuration Access is limited to 2<sup>25</sup> clock cycles. PCI Express: 1s -> max. 2.8 KB

#### • Programming interface:

The data can be written byte, word or dword at a time. All combinations of byte-enables of the PCI specification are supported. The starting byte could be anywhere within a page. When the end of the page is reached, the address wraps around to the beginning of the same page and the data will be stored there. This means that the Software is capable to handle the sector and page borders that no data are lost.

Note: The same byte can't be reprogrammed without erasing the whole sector first.

#### Support of SPI Flash Memories of different vendors:

The current SPI Flash Memory devices of different vendors vary in their Instruction-Codes for the read ID instruction. After reset the used SPI Flash Memory needs to be identified by the SPI Flash Memory Loader. The identification of the Flash on the board after **PERSTn** should look like this:

- after the release of PERSTn the SPI Flash Memory Loader starts directly to read the Configuration Data. If

the SPI Flash Memory is programmed the loader reads all data into the Register-File until key (0x55) cannot be found anymore. Then and also if the SPI Flash Memory was not programmed at all the loader

moves to an idle state to wait for new commands.

- Afterwards the Software identifies the Flash. Therefore the Vendor- and Device-ID are read out of the SPI Flash Memory and the memory type is stored in the RD ID Protocol bit in SPI Flash Memory Control Register.

Depending on the EPROM type the software uses different instruction code sets (SPI Flash Memory Opcode 1 and 2 Register).

Even during identification of the SPI Flash Memory there are two possible protocols to be used. Maybe both protocols must be tried by software to read out the SPI Flash Memory ID.

#### Sector Erase:

Due to the fact that the Flash is divided into sectors only, a write to the VPD or configuration region leads to the erasure and rewriting of the whole VPD/configuration information.

Reprogrammable VPD during operation of the device can be achieved by the use of an additional TWSI EEPROM (see chapter 2.5 TWSI EEPROM on page 22).

- · Supported Instructions for the SPI Flash Memory:

- Write Program Data into Memory Array

- Chip Erase Erase All Sectors in Memory Array

- Sector Erase Erase One Sector in Memory Array

- WREN

Set Write Enable Latch has to be set before Program, Chip- and Sector-Erase

- Read Read Data from Memory Array

- RDSR Read Status Register

- RDID Read Vendor and Device ID (two different protocols)

- NOP No Operation

### 2.5 TWSI EEPROM

The TWSI EEPROM is an external memory device for VPD (vital product data).

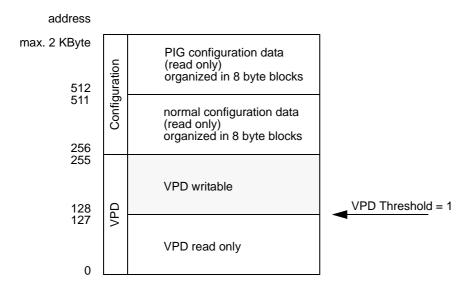

Its address space is divided into two parts (see Figure 4).

Figure 4: Internal Structure of TWSI EEPROM.

Within the lower address region (0 to 255) the VPD is located. This part contains the read only and writable section of VPD separated by VPD Threshold (see **VPD Write Thr** in Our Register 2 in chapter 3.2.4.1 Our Register 1 and Our Register 2 on page 69).

In higher addresses the configuration data is stored which is loaded automatically into the ASIC after PERSTn with its internal TWSI EEPROM Loader (see chapter 2.6 TWSI EEPROM Loader on page 23).

Two different configurations may be loaded by the TWSI EEPROM Loader depending on the current operation mode "normal" or "Plug in Go".

Normally this feature is not used due to the existence of the SPI Flash Memory, which also holds configuration data.

The TWSI EEPROM is read and written to via TWSI bus. Its TWSI address is 0b101000.

The size of the TWSI EEPROM, the amount of writable VPD area and the Device Select Byte used for VPD TWSI accesses are determined by the read only fields **VPD ROM Size**, **VPD Write Threshold** and **VPD Devsel**<sup>1</sup> in **Our Register 2** (see chapter 3.2.4.1 Our Register 1 and Our Register 2 on page 69). These fields can be reloaded from the SPI Flash Memory, if another device is used.

For manufacturing programming of the read only part of the TWSI EEPROM, Testmode (**En Config Write**) must be set. Then the whole TWSI EEPROM is writable. Programming of the TWSI EEPROM is managed with ASIC internal registers **VPD Address** and **VPD Data** (see chapter 3.2.4.10 VPD Address Register on page 78 and chapter 3.2.4.11 VPD Data Register on page 78).

After the next power cycle the read only areas within the TWSI EEPROM are write protected again

Doc. No. MV-S102130-00, Rev. -- CONFIDENTIAL Copyright © 2004 Marvell

<sup>1.</sup> Hint: VPD Devsel must not be overwritten via TWSI EEPROM in absence of the SPI flash memory. This may lead to a complete damage of the board (TWSI EEPROM must be changed afterwards!!!

Page 23

#### TWSI EEPROM Loader 2.6

The TWSI EEPROM Loader looks for configuration data within the external TWSI EEPROM, although the configuration data is stored within the SPI Flash Memory and therefore no data is to be read out normally.

- The TWSI EEPROM Loader is active once after the execution of the SPI Flash Memory Loader (after PER-STn).

- It works analogously to the SPI Flash Memory Loader and loads startup data into the Configuration and Control Register File (where needed):

- The loader is capable of accessing potentially all registers in the Control Register File space.

- Register address and data are stored in 8-byte entries in the TWSI EEPROM (see Table 15 for details).

- The 8-byte entries are located on 8-byte boundaries up from address 256 of the TWSI EEPROM in increasing order. Each entry is marked with a key byte (0x55).

Data format of first 8 byte block within TWSI EEPROM Table 15:

| TWSI access cycle number | TWSI EEPROM Address | contents    |         |

|--------------------------|---------------------|-------------|---------|

| 2                        | 0x107               | Data<3>     |         |

|                          | 0x106               | Data<2>     |         |

|                          | 0x105               | Data<1>     |         |

|                          | 0x104               | Data<0>     |         |

| 1                        | 0x103               | Address/upp | per     |

|                          | 0x102               | Address/low | er      |

|                          | 0x101               | reserved    | BE<0:3> |

|                          | 0x100               | Key = 0x55  |         |

- The ASIC internal registers may be written with dword, word or byte accesses.

- If started, the loader reads subsequent entries starting with the initial value of the TWSI EEPROM Address Counter (see 3.2.4.12 TWSI EEPROM Control Register on page 79) as long as a valid key is found.

- Loading is started by finishing the SPI Flash Memory Loader state machine or by setting the Flag to start the TWSI EEPROM Loader (see 3.2.4.12 TWSI EEPROM Control Register on page 79).

- Loading the TWSI EEPROM via Flag in the TWSI EEPROM Control Register is intended for testing purposes only. It is not recommended to reload the Configuration Register File using this command.

- While loading, accesses to any resource of the network adapter are terminated by Target Retry Cycles.

- The transferred data after PERSTn in this way is limited to fulfill the requirements of PCI bus<sup>1</sup>.

- This time consuming reading via TWSI bus may be deactivated by setting the Flag bit to stop (0) in the TWSI EEPROM Control Register see 3.2.4.12 TWSI EEPROM Control Register on page 79. Then the state machine does not even start reading values.

- Transformation of the TWSI EEPROM data (8 bytes) into multiple byte/dword memory read accesses from the

- 32-bit read data is received via TWSI-Bus within one read access. Two read accesses are necessary to receive the full information for writing one internal register.

- Programming the TWSI EEPROM is described in chapter 2.5 TWSI EEPROM on page 22

Copyright © 2004 Marvell CONFIDENTIAL Doc. No. MV-S102130-00, Rev. --Document Classification: Proprietary Information

<sup>1.</sup> T<sub>rhfa</sub> PERSTn High to First configuration Access is limited to 2<sup>25</sup> clock cycles. PCI Express: 1s -> max. 2.8 KB

## 2.7 Plug In Go Unit

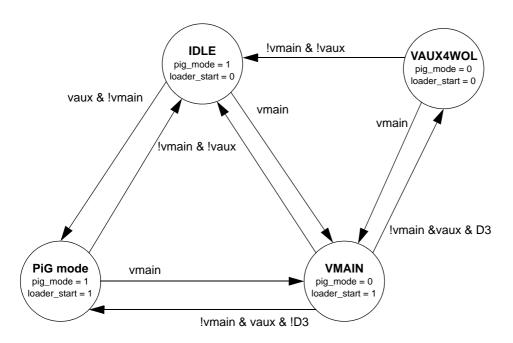

The Plug In Go unit decides wether to load normal configuration or PiG configuration by the SPI Flash Memory Loader.

Which configuration to select is dependent on the available voltages  $V_{main}$  and  $V_{aux}$  and if the device is in the D3 state.

The Plug in Go configuration is loaded by the SPI Flash Memory loader when  $V_{main}$  is no longer available but  $V_{aux}$  and the device is not in D3 state.

After a power on (both voltages not available) PiG configuration is loaded when only  $V_{aux}$  available. Else normal configuration is loaded by the SPI Flash Memory loader.

See figure below for the complete state description of the Plug in Go unit:

Figure 5: Plug in Go Unit State Diagram

loader\_start = 1 causes the SPI Flash Memory loader to load the configuration once after entering the state

pig\_mode = 0: normal configuration is loaded by the SPI Flash Memory loader

pig\_mode = 1: Plug in Go configuration is loaded by the SPI Flash Memory loader

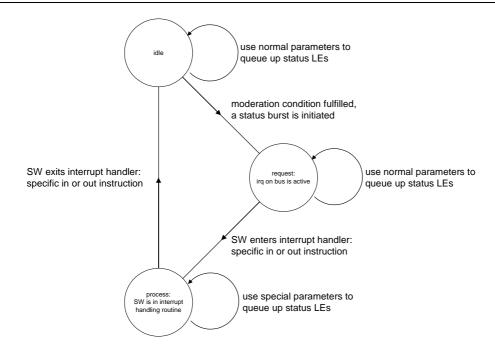

## 2.8 Interrupts

Chip internal interrupt handling is done with the following internal signals:

- irq is asserted when at least one of the unmasked interrupt sources is active (interrupt).

When irq is not asserted, then none of the unmasked interrupt sources is active or internal interrupt masking line isr mask is active.

- isr\_status is asserted (set to '1') when entering the interrupt service routine: "ISR mode".

isr\_status is deasserted (set to '0') when leaving the interrupt service routine: "normal mode".

- isr\_mask shows if currently all interrupts are masked (regardless of interrupt mask register settings).

The two internal signals irg and isr\_status show the current state of interrupt processing:

| Table 16: | Interrupt Proc | Interrupt Processing Signals |  |  |  |  |

|-----------|----------------|------------------------------|--|--|--|--|

|           |                |                              |  |  |  |  |

| irq | isr_status | interrupt<br>state | comment                                                                         |

|-----|------------|--------------------|---------------------------------------------------------------------------------|

| 0   | 0          | idle               | No interrupt request is pending                                                 |

| 1   | 0          | request            | Interrupt pending, but not yet in process                                       |

| 0   | 1          | processing         | Interrupt is served but not yet fin-<br>ished.<br>All further interrupts masked |

**isr\_status** is used by the status BMU to accelerate the processing according to the threshold settings for the status FIFO during interrupt processing.

The **Interrupt Source Register** holds the interrupts of all resources (see chapter 3.3.2.4 Interrupt Source Register on page 130).

Each interrupt is maskable by the **Interrupt Mask Register** (see chapter 3.3.2.5 *Interrupt Mask Register* on page 131).

All unmasked interrupts are Or'ed and propagated to the internal interrupt line irq.

Interrupts generated by hardware checks are readable via the **Interrupt Hardware Error Source Register** (see chapter 3.3.2.6 Interrupt HW Error Source Register on page 131). Each interrupt is maskable by the **Interrupt Hardware Error Mask Register** (see chapter 3.3.2.7 Interrupt HW Error Mask Register on page 132). All unmasked interrupts are Or'ed and propagated to the **Interrupt Source Register** as **Interrupt Hardware Error**.

The interrupts from the MAC are readable from the **MAC Interrupt Source Registers** (see chapter 3.3.2.54 MAC Interrupt Source Register on page 201). Each interrupt is maskable by the **MAC Interrupt Mask Registers** (see chapter 3.3.2.55 MAC Interrupt Mask Register on page 202). All unmasked interrupts are Or'ed and propagated to the **Interrupt Source Register** as **MAC Interrupt.**

An interrupt from a masked source can still be read from its Source Register.

April 20, 2004, Advanced

An interrupt is cleared and/or disabled as stated in the description of the related interrupt resource.

The **Special Interrupt Source Registers** mirror the **Interrupt Source Register** with special functionality adapted to typical SW handling:

Copyright © 2004 Marvell CONFIDENTIAL Doc. No. MV-S102130-00, Rev. --

- Special Interrupt Source Register 1:

- If the internal interrupt line **irq** is asserted, the read value is the same as in the **Interrupt Source Register**. If the internal interrupt line **irq** is NOT asserted, the read value is 0.

- If the internal interrupt line <code>irq</code> is asserted, reading the <code>Special Interrupt Source Register 1</code> masks all interrupts. As a result the internal interrupt line <code>irq</code> is deasserted.

- Special Interrupt Source Register 2:

- If the internal interrupt line **irq** is asserted, the read value is the same as in the **Interrupt Source Register**. If the internal interrupt line **irq** is NOT asserted, the read value is 0.

- If the internal interrupt line **irq** is asserted, reading the **Special Interrupt Source Register 2** masks all interrupts and sets **isr\_status** flag to "ISR mode". As a result the internal interrupt line **irq** is deasserted.

- Special Interrupt Source Register 3:

- If the internal interrupt line **irq** is asserted, the read value is the same as in the **Interrupt Source Register**. If the internal interrupt line **irq** is NOT asserted, the read value is 0.

- Reading the **Special Interrupt Source Register 3** always masks all interrupts. As a result the internal interrupt line **irq** is deasserted.

- If the internal interrupt line irq is asserted, isr\_status flag is set to "ISR mode".

Table 17: Effects on reading the Special Interrupt Source Registers

|                                  | Special                    | Special                     | Special                     |

|----------------------------------|----------------------------|-----------------------------|-----------------------------|

|                                  | Interrupt                  | Interrupt                   | Interrupt                   |

|                                  | Source                     | Source                      | Source                      |

|                                  | Register 1                 | Register 2                  | Register 3                  |

| Read value when irq asserted     | Interrupt                  | Interrupt                   | Interrupt                   |

|                                  | Source                     | Source                      | Source                      |

|                                  | Register                   | Register                    | Register                    |

| Read value when irq not asserted | 0                          | 0                           | 0                           |

| isr_status set to "ISR mode"     | -                          | when <b>irq</b> is asserted | when <b>irq</b> is asserted |

| Masking of all interrupts        | only, when irq is asserted | only, when irq is asserted  | always                      |

| internal <b>irq</b> line         | deasserted                 | deasserted                  | deasserted                  |

|                                  | after-                     | after-                      | after-                      |

|                                  | wards                      | wards                       | wards                       |

All interrupts can be moderated by the IRQ Moderation Timer.

Moderation is controllable individually for each interrupt by the Interrupt Moderation Mask Registers.

There are two modes of signaling interrupts (internal interrupt line irq is active) to the host system:

Via Interrupt line INTAn: The internal signal irq is forwarded to the PCI signal INTA# (unless inhibited by register setting).

Doc. No. MV-S102130-00, Rev. -- CONFIDENTIAL Copyright © 2004 Marvell

Via MSI (Message Signaled Interrupt):

The MSI agent notifies the interrupt via busmaster write to the defined host memory address.

When leaving the ISR and all interrupt sources have been cleared, the MSI agent is in state idle and waits for new interrupts. If there are still active interrupt sources or a new interrupt source is set to active, irq is asserted again and the MSI agent is triggered for a new interrupt request.

The mode is selected with MSI Enable bit in MSI Message Control register.

#### 2.8.1 IRQ Moderation Timer

The IRQ Moderation Timer (see chapter 3.3.2.29 IRQ Moderation Timer Registers on page 147) is a programmable 32-bit downcounter with a resolution of one core clock cycle (6.4 ns,  $T_{max} = 21.47$  s) for the usage as time-base for IRQ Moderation.

The command Interrupt Moderation Timer Start loads Interrupt Moderation Timer with Interrupt Moderation Timer Init Value and starts counting down.

Reaching ZERO or loaded with ZERO the Interrupt Moderation Timer is reloaded with Interrupt Moderation Timer Init Value.

The Interrupt Moderation Timer controls the assertion of the internal interrupt line irq by gating the interrupts as defined by the Interrupt Moderation Mask Registers. If the Interrupt Moderation Timer is stopped or reaches ZERO, the gate opens and allows the masked interrupts to propagate to the bus. The assertion of irq has been caused by one of the masked interrupts, therefore delayed until the next time, the Interrupt Moderation Timer reaches ZERO. irq is kept asserted until the appropriate operation of clearing the interrupt request is completed. The deassertion of irq is not affected.

The Interrupt Moderation Timer may be stopped by the command Interrupt Moderation Timer STOP.

While **HW Reset** or **SW Reset** the **Interrupt Moderation Timer** is stopped and the gate is closed. After releasing **SW Reset** the gate is initially open until the **Interrupt Moderation Timer** is loaded with a value other than ZERO and started.

## 2.8.2 Message Signaled Interrupts (MSI)

Reporting interrupts to the host system via MSI is done, when the **MSI Enable** bit is set in **MSI Message Control** Register. Interrupt line INTA# is not used in this mode.

This chip is capable of handling one MSI message. This is specified also in the MSI control register.

The location for the MSI message is defined in register MSI Message Address Upper/Lower (64 bit). At this location within the host memory the interrupt message of the chip is written to.

The message itself is stored within register MSI message data register.

The MSI agent detects an active internal interrupt line **irq** and starts a busmaster write to the defined **MSI address** with the defined **MSI message data**.

The host system now detects a MSI message at the defined location and starts an interrupt service routine.

During the ISR all interrupts are masked.

After completion of the ISR the interrupts are unmasked again and the **irq** line is released in case of solving all interrupt reasons during the ISR. Otherwise the interrupt is signaled again to the host.

## 2.9 Buffer Management Units (BMU)

The Buffer Management Units are the interface for the Bus Interface Unit (BIU) to the queues.

The internal requests are presented as one for each queue.

Guaranteed length of transferable data is derived from the data provided by the BMU and the FIFO.

The Master Backends are also providing the multiplexers for positioning of data words at the right byte lanes on misaligned transfers and to revert byte ordering for descriptor words depending on **Rev Bytes Desc**.

The position of the multiplexers are controlled by the BMUs.

## 2.9.1 Format of Descriptor and Status List Elements

Communication between host and PCI device is done via interchanged list elements provided by the host within its memory space.

Chip internal descriptors can be modified via list elements and control functions are initiated or status information is reported.

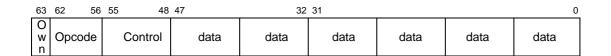

All list elements of the different agents are based on the same structure (see figure below):

- Width of the list elements is always 64 bit

- Bit 63 is the own bit: it marks the ownership of the list element:

- 1: the PCI device is owner of the list element

- 0: the host is owner of the list element

- The following 7 bits (bit 62... bit 56) contain the opcode for this list element.

The opcode defines the meaning of the remaining fields of the list element.

The different opcodes are assigned to the different tasks as follows:

Table 18: Opcode Assignments

| Opcode (hex) | Task group                       |

|--------------|----------------------------------|

| 0x00 - 0x0f  | not defined                      |

| 0x10 - 0x1f  | TCP Sum Parameter or Function    |

| 0x20 - 0x2f  | Register Updates for RX and TX   |

| 0x30 - 0x3f  | not defined                      |

| 0x40 - 0x4f  | DMA for RX and TX                |

| 0x50 - 0x5f  | not defined                      |

| 0x60 - 0x6f  | Status List Functions            |

| 0x70 - 0x7f  | Special Actions (e.g. put index) |

- The control field (bit 55.. bit 48) specifies additional attributes of the list element

- The remaining 48 bits (bit 47.. bit 0) hold data according to the opcode and control information.

Figure 6: Base Format of the List Elements

The list elements of each task group are described in detail within the according chapters.

## 2.9.1.1 Receive Descriptor List Element

Figure 7 shows all different list elements processable by the RX BMU.

### Figure 7: RX Descriptor List Element Definition

| 63          | 62 56                   | 55 48    | 47 32         | 31 0                            |

|-------------|-------------------------|----------|---------------|---------------------------------|

| O<br>w<br>n | w Opcode control        |          | buffer length | buffer address low dword        |

| 63          | 62 56                   | 55 48    | 47 32         | 31 0                            |

| O<br>w<br>n | Opcode<br><b>Buffer</b> | control  | buffer length | buffer address low dword        |

| 63          | 62 56                   | 55 48    | 47 32         | 31 0                            |

| O<br>w<br>n | Opcode<br>ADDR64        | reserved | reserved      | buffer address high dword       |

| 63          | 62 56                   | 55 48    | 47 32         | 31 0                            |

| O<br>w<br>n | Opcode<br>TCPPAR        | reserved | reserved      | TCP Start Sum 1 TCP Start Sum 2 |

The following opcodes are valid for RX descriptor list elements:

Table 19: RX descriptor list element valid opcodes

| Opcode<br>(hex) 7 bit | Opcode Name                | Description of assigned list element                                                                                                                                                                                                                      |

|-----------------------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x12                  | TCPPAR                     | Bits 31:0: TCP Sum Start Address 1 and 2                                                                                                                                                                                                                  |

| 0x21                  | ADDR64                     | Bits 31:0: New value for the Buffer Address High Register of the RX BMU                                                                                                                                                                                   |

| 0x40                  | Buffer                     | Follow up buffer for a packet Bits 55:48: buffer control bits Bits 47:32: buffer length Bits 31:0: buffer address low One buffer list element must be skipped on the start of a new packet. It enables a DMA request by the RX BMU to write receive data. |

| 0x41                  | Packet                     | First buffer of a packet  Bits 55:48: buffer control bits  Bits 47:32: buffer length  Bits 31:0: buffer address low  A packet list element enables a DMA request by the  RX BMU to write receive data.                                                    |

| other                 | not supported by RX<br>BMU | Processing of list elements is stopped and an interrupt IRQ is asserted by BMU.                                                                                                                                                                           |

The Own bit signals the ownership of the list element:

- Own = 1: The PCI device is owner of the list element

- Own = 0: If Own = 0 in a list element detected by the BMU, it stops processing list elements and asserts an interrupt request IRQ.

The Control field defines attributes to the descriptor:

**Table 20: Control Field Definitions**

| bit<br># | Control bit | Meaning (when set to 1)                        |

|----------|-------------|------------------------------------------------|

| 7        | reserved    |                                                |

| 6        | FRC_STAT    | List element forces a burst of the Status FIFO |

| 5:2      | reserved    |                                                |

| 1        | CALSUM      | Calculate checksum for this packet             |

| 0        | reserved    |                                                |

### 2.9.1.2 Transmit Descriptor List Element

Figure 8 shows all different list elements processable by the TX BMU. If not mentioned explicitly the ordering is little endian.

Figure 8: TX Descriptor List Element Definition

| O pcode n         Opcode Packet         Control         buffer length         buffer address low dword           63         62         56         55         48         47         32         31         0           O pcode w Large In Send         Control         buffer length         buffer address low dword         0           63         62         56         55         48         47         32         31         0           63         62         56         55         48         47         32         31         0           63         62         56         55         48         47         32         31         0           63         62         56         55         48         47         32         31         0           63         62         56         55         48         47         32         31         0           63         62         56         55         48         47         32         31         0           Co pcode n ceserved         VLAN (big endian)         reserved         vLAN (big endian)         buffer address high dword           63         62         56         55         48                                                                                                                                                                                        | 63  | 62          | 56 | 55 48      | 3 47         | 32            | 31  |               |                   | 0 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------------|----|------------|--------------|---------------|-----|---------------|-------------------|---|

| O w Large Send         Control Send         buffer length         buffer address low dword           63 62 56 55 48 47         32 31         0           O Opcode N Buffer         Control Control Control Control Buffer length         buffer address low dword           63 62 56 55 48 47         32 31         0           63 62 56 55 48 47         32 31         0           63 62 56 55 48 47         32 31         0           63 62 56 55 48 47         32 31         0           63 62 56 55 48 47         32 31         0           63 62 56 55 48 47         32 31         0           63 62 56 55 48 47         32 31         0           63 62 56 55 48 47         32 31         0           63 62 56 55 48 47         32 31         0           63 62 56 55 48 47         32 31         0           63 62 56 55 48 47         32 31         0           63 62 56 55 48 47         32 31         0           63 62 56 55 5 48 47         32 31         0           63 62 56 55 5 48 47         32 31         0           63 62 56 55 48 47         32 31         0           63 62 56 55 48 47         32 31         0           63 62 56 55 48 47         32 31         0 <td>W</td> <td></td> <td></td> <td>Control</td> <td></td> <td>buffer length</td> <td></td> <td>buffer addre</td> <td>ss low dword</td> <td></td> | W   |             |    | Control    |              | buffer length |     | buffer addre  | ss low dword      |   |

| O w Large Send         Control Send         buffer length         buffer address low dword           63 62 56 55 48 47         32 31         0           O Opcode N Buffer         Control Control Control Control Buffer length         buffer address low dword           63 62 56 55 48 47         32 31         0           63 62 56 55 48 47         32 31         0           63 62 56 55 48 47         32 31         0           63 62 56 55 48 47         32 31         0           63 62 56 55 48 47         32 31         0           63 62 56 55 48 47         32 31         0           63 62 56 55 48 47         32 31         0           63 62 56 55 48 47         32 31         0           63 62 56 55 48 47         32 31         0           63 62 56 55 48 47         32 31         0           63 62 56 55 48 47         32 31         0           63 62 56 55 48 47         32 31         0           63 62 56 55 5 48 47         32 31         0           63 62 56 55 5 48 47         32 31         0           63 62 56 55 48 47         32 31         0           63 62 56 55 48 47         32 31         0           63 62 56 55 48 47         32 31         0 <td></td>                                              |     |             |    |            |              |               |     |               |                   |   |

| Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     | _           |    | 55 48      | 3 47         | 32            | 31  |               |                   | 0 |

| O w n         Opcode Buffer         Control         buffer length         buffer address low dword           63         62         56         55         48         47         32         31         0           O Docode W ADDR64         reserved         reserved         buffer address high dword         0           63         62         56         55         48         47         32         31         0           63         62         56         55         48         47         32         31         0           63         62         56         55         48         47         32         31         0           O Docode W ADDR64         reserved         VLAN (big endian)         reserved         vlan         0           O Opcode W ADDR64         reserved         VLAN (big endian)         buffer address high dword         0           63         62         56         55         48         47         32         31         0           O Opcode W LRGLEN n + VLAN         reserved         VLAN (big endian)         reserved         large send segment length                                                                                                                                                                                                                                      | W   | Large       | ,  | Control    |              | buffer length |     | buffer addre  | ss low dword      |   |

| W   Opcode Buffer   Control   buffer length   buffer address low dword                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 63  | 62          | 56 | 55 48      | 3 47         | 32            | 31  |               |                   | 0 |

| O w ADDR64         reserved         reserved         buffer address high dword           63 62 56 55 48 47         32 31         0           O Opcode In Carden Pocket         reserved         reserved         large send length           63 62 56 55 48 47         32 31         0           O Opcode In VLAN (big endian)         reserved         reserved           63 62 56 55 48 47         32 31         0           O Opcode In VLAN (big endian)         reserved         VLAN (big endian)           63 62 56 55 48 47         32 31         0           O Opcode In VLAN (big endian)         buffer address high dword           63 62 56 55 48 47         32 31         0           O Opcode In VLAN (big endian)         reserved         large send segment length           63 62 56 55 48 47         32 31         0           O Opcode In VLAN (big endian)         reserved         large send segment length           63 62 56 55 48 47         32 31         0           O Opcode In VLAN (big endian)         reserved         TCP sum write                                                                                                                                                                                                                                                                     | W   |             |    | Control    |              | buffer length |     | buffer addre  | ss low dword      |   |

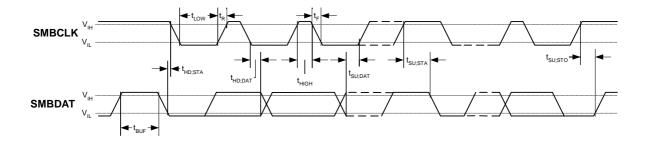

| Opcode   reserved   reserved   buffer address high dword                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 63  | 62          | 56 | 55 48      | 3 47         | 32            | 31  |               |                   | 0 |